Thảo luận:Điện số/Bộ phận điện số/Bộ dời Bit

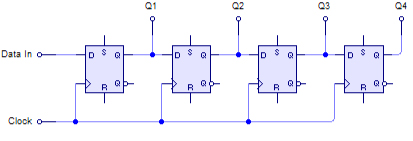

Thêm đề tàiNhập Nối Tiếp , Xuất Song Song - Serial-in, parallel-out

[sửa]This configuration allows conversion from serial to parallel format. Data are input serially, as described in the SISO section above. Once the data has been input, it may be either read off at each output simultaneously, or it can be shifted out and replaced.

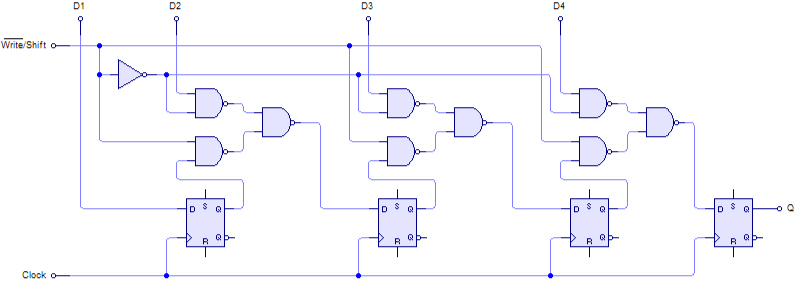

Nhập Song Song , Xuất Nối Tiếp - Parallel-in, serial-out

[sửa]This configuration has the data input on lines D1 through D4 in parallel format. To write the data to the register, the Write/Shift control line must be held LOW. To shift the data, the W/S control line is brought HIGH and the registers are clocked. The arrangement now acts as a SISO shift register, with D1 as the Data Input. However, as long as the number of clock cycles is not more than the length of the data-string, the Data Output, Q, will be the parallel data read off in order.

The animation below shows the write/shift sequence, including the internal state of the shift register.