Sách điện số/Bộ phận điện số đồng bộ/Bộ nhớ điện số

Giao diện

Bộ nhớ điện số

[sửa]Tạo từ mạch điện của 2 NAND hay 2 NOR có 2 trạng thái ổn

NAND Flip Flop

[sửa]NOR Flip Flop

[sửa]

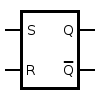

SR latch operation S R Action 0 1 Q = 1 1 0 Q = 0 1 1 Keep state SR Register

[sửa]Enable S R Q Q 0 0 0 Latch 0 0 1 Latch 0 1 0 Latch 0 1 1 Latch 1 0 0 Latch 1 0 1 0 1 1 1 0 1 0 1 1 1 Metastable

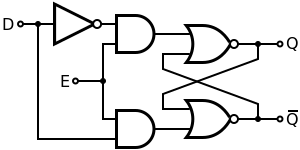

D register

[sửa]Enable D Q Q 0 0 Latch 0 1 Latch 1 0 0 1 1 1 1 0

and can be described either of the following tables:

T register

[sửa]Characteristic table T Q Qnext Comment 0 0 0 Hold state 0 1 1 1 0 1 Toggle 1 1 0 Excitation table Q Qnext T 0 0 0 0 1 1 1 0 1 1 1 0 JK register

[sửa]Characteristic table J K Qnext Comment 0 0 Qprev Hold state 0 1 0 Reset 1 0 1 Set 1 1 Qprev Toggle

Excitation table Q Qnext J K Comment 0 0 0 X Hold state 0 1 1 X Set 1 0 X 1 Reset 1 1 X 0 Hold state